Der Fokus von D2 liegt daher auf programmierbaren Switches und programmierbaren Netzwerkkarten (im weiteren INP-Plattformen genannt), die eine Ausführung von Anwendungsfunktionen direkt in der Netzwerk-Hardware ermöglichen. Die aktuell verfügbaren INP-Plattformen besitzen allerdings noch wesentliche Limitierungen: (1) Anwendungslogik vs. Leistung: Aktuell existieren unterschiedliche Ansätze für INP-Plattformen. Auf der einen Seite sind hier Ansätze wie der Barefoot Tofino zu nennen, die INP-Funktionen bei hohen Leistungsraten von bis zu 100 Gbps Ethernet ausführen können, aber nur eine eingeschränkte Programmierung mittels P4 bieten. Auf der anderen Seite existieren INP-Plattformen, die mittels Sprachen wie Micro C eine generelle Programmierbarkeit bieten, aber häufig nur limitierte Leistungsraten wesentlich unter 100 Gbps erreichen. (2) Verteilte Ausführung und Mandantenfähigkeit: Ein wichtiges Einsatzgebiet von INP-Plattformen sind Cloud-Rechenzentren. In heutigen Cloud-Rechenzentren bilden Netzwerk-Switches (und -Karten) typischerweise eine komplexe Netzwerk-Topologie, wobei die Netzwerk-Hardware von mehreren Mandanten geteilt genutzt wird. Allerdings werden diese beiden Aspekte (verteilte Ausführung und Mandantenfähigkeit) durch heutige INP-Plattform nicht bzw. nur sehr limitiert unterstützt. (3) Dienstgüte-Garantien: Aktuelle INP-Plattformen bieten Anwendungen nur limitierte Möglichkeiten, Dienstgüte-Garantien bei der Ausführung von INP-Funktionen zu spezifizieren. Dies erschwert die Unterstützung von missionsentscheidenden Anforderungen durch INP.

Im Rahmen von D2 soll daher eine neue Hardware-Architektur für INP-Plattformen erforscht werden, die FPGA-basierte rekonfigurierbare Hardware-Beschleuniger verwendet. Damit können nicht nur komplexere Anwendungsfunktionen wie z. B. iterative Berechnungen realisiert werden, sondern auch die zuvor genannten Einschränkungen adressiert werden. Beispielsweise soll die FPGA-basierte INP-Plattform es ermöglichen, auch komplexe INP-Funktionen bei hohen Leistungsraten von bis zu 100 Gbps auszuführen. Die neue FPGA-basierte INP-Plattform soll in D2 anhand unterschiedlicher Szenarien evaluiert werden. Im Vordergrund steht dabei der Einsatz der INP-Plattform zur Beschleunigung typischer Anwendungen innerhalb von Cloud-Rechenzentren (z. B. AI und Big Data-Systeme wie Spark oder Tensorflow), für die eine effiziente Nutzung von INP wesentliche Vorteile verspricht. Die in D2 entstehende Hardware-Technologie soll aber auch einen breiteren Einsatz auch jenseits von Cloud Rechenzentren ermöglichen (z. B. für Edge-Szenarien in C2), weshalb sie im Rahmen des erweiterten INP-Testbeds ganz MAKI zur Nutzung zur Verfügung gestellt wird.

Die im Rahmen der Anschubfinanzierung entwickelte Hardware-beschleunigte INP-Plattform kann als INP-Switch oder auch als INP-fähige Netzwerkkarte verwendet werden. Allerdings verfügt die prototypische INP-Plattform noch über keine Hardware-Transitionen, um die INP-Funktionalität dynamisch an unterschiedliche Anwendungen anzupassen. Dies ist nicht nur notwendig, um im laufenden Netzbetrieb neue Anwendungen zu unterstützen, sondern auch um die INP-Funktionen dynamisch auf mehrere Switches zu verteilen bzw. die Hardware-Ressourcen an die geforderten Dienstgüte-Garantien anzupassen. In Phase III soll daher aufbauend auf den initialen Ergebnissen aus Phase II eine transitionsfähige Hardware-beschleunigte INP-Plattform erforscht werden. Ein wesentlicher Fokus von D2 ist dabei, wie die Hardware-beschleunigte INP-Funktionalität auch Anwendungsexperten ohne Kenntnisse des FPGA-Entwurfs zugänglich gemacht werden kann. Dazu wird D2 an einer Programmiersprache forschen, die es Anwendungsexperten ermöglicht, auch komplexe INP-Funktionen zu spezifizieren. Ebenfalls werden in D2 passende Programmierwerkzeuge wie Compiler erforscht, die dann automatisiert aus diesen Beschreibungen die Transitionslogiken auf Hardware-Ebene konstruieren können.

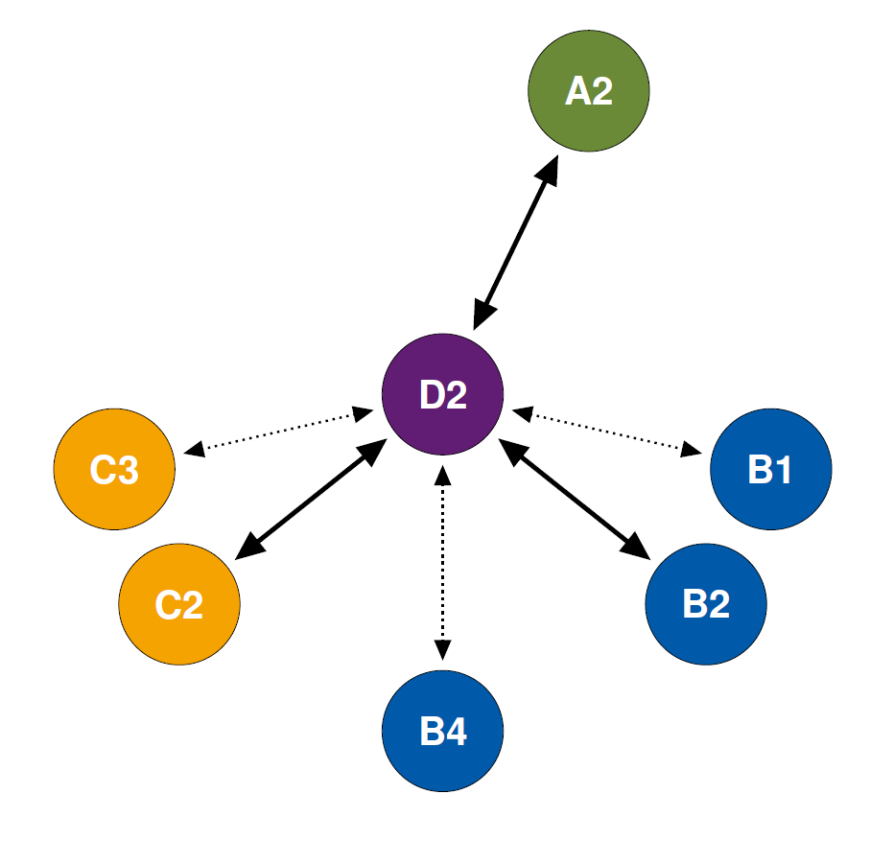

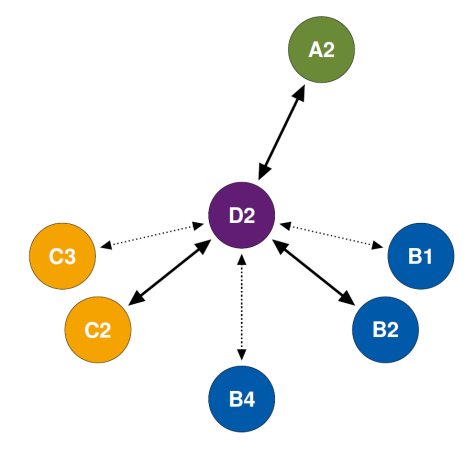

Im Teilprojekt D2 werden für MAKI daher wesentliche Beiträge zur automatischen Konstruktion von Transitionslogiken zur Anpassung des Netzwerkes bis auf die Hardware-Ebene geleistet. Darüber hinaus spielen aber auch Aspekte eine wichtige Rolle, wie missionsentscheidende Anforderungen durch Hardware-Transitionen besser unterstützt werden können und wie kooperative Hardware-Transitionen zur Anpassung der INP-Funktionen über mehrere INP-Plattformen hinweg genutzt werden können. Die in D2 entwickelten Ansätze ermöglichen diverse Kooperationen mit unterschiedlichen Teilprojekten in Phase III aus allen Projektbereichen. Um die in D2 entwickelte Technologie durch andere Teilprojekte nutzbar zu machen, wird das MAKI-weite Testbed um die entsprechende INP-Funktionalität erweitert.